# TWL3016

GSM/DCS Baseband and Voice A/D and D/A RF Interface Circuit With Power Supply Management

# Data Manual

# TWL3016 GSM/DCS Baseband and Voice A/D and D/A RF Interface Circuit With Power Supply Management

Data Manual

Literature Number: SWCS010 November 2003

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products & application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

# **Contents**

| Se | ection |           | Title                                   | Page |

|----|--------|-----------|-----------------------------------------|------|

| 1  | Introd | luction . |                                         | 1–1  |

|    | 1.1    |           | otion                                   |      |

|    | 1.2    | Feature   | es                                      | 1–1  |

|    | 1.3    | Tradem    | narks                                   | 1–2  |

|    | 1.4    | Orderin   | ng Information                          | 1–2  |

| 2  | Termi  | nal Desc  | criptions                               | 2–1  |

| 3  | Funct  | ional De  | escription                              | 3–1  |

|    | 3.1    | Audio C   | Codec                                   | 3–3  |

|    | 3.2    | Baseba    | and Codec                               | 3–3  |

|    | 3.3    | Low-Dr    | opout Linear Voltage Regulator          | 3–3  |

|    | 3.4    | Backup    | Battery Switch                          | 3–4  |

|    | 3.5    | SIM Ca    | ard Shifters (SIMS)                     | 3–4  |

|    | 3.6    | Monitor   | ring ADC                                | 3–4  |

|    | 3.7    | •         | Reference/Power-On Control              |      |

|    | 3.8    | Baseba    | and Serial Port                         | 3–4  |

|    | 3.9    |           | erial Port                              |      |

|    | 3.10   | Microco   | ontroller Serial Port                   | 3–5  |

|    | 3.11   |           | and Serial Port                         |      |

|    | 3.12   | Stereo    | Audio (I2S) Serial Port                 | 3–5  |

|    | 3.13   |           | atic Frequency Control                  |      |

|    | 3.14   | Automa    | atic Power Control                      | 3–5  |

|    | 3.15   |           | y DAC                                   |      |

|    | 3.16   | -         | oltage (20 V) Battery Charger Interface |      |

| 4  |        |           | ription                                 |      |

|    | 4.1    |           | Codec                                   |      |

|    |        | 4.1.1     | Voice Uplink Path                       |      |

|    |        | 4.1.2     | Voice Downlink Path                     |      |

|    |        | 4.1.3     | Stereo Audio Path                       |      |

|    | 4.2    |           | and Uplink and Downlink Path            |      |

|    |        | 4.2.1     | Baseband Uplink Path                    |      |

|    |        | 4.2.2     | Baseband Downlink Path                  |      |

|    | 4.3    |           | opout Voltage Regulators                |      |

|    |        | 4.3.1     | RDBB                                    | 4–9  |

|    |        | 4.3.2     | RRAM                                    | 4–9  |

|    |        | 4.3.3     | RMEM                                    | 4–9  |

|    |        | 4.3.4     | -                                       | 4–10 |

|    |        | 4.3.5     | RABB                                    | 4–10 |

|   |      | 4.3.6      | RUSB                                                                            | 4–10  |

|---|------|------------|---------------------------------------------------------------------------------|-------|

|   |      | 4.3.7      | RSIM                                                                            | 4–10  |

|   |      | 4.3.8      | RRTC                                                                            | 4–10  |

|   | 4.4  | SIM Card   | d Digital Interface                                                             | 4–12  |

|   | 4.5  | Monitorin  | ng ADC                                                                          | 4–12  |

|   | 4.6  | Reference  | ce Voltage and Power Control                                                    | 4–13  |

|   |      | 4.6.1      | Block Descriptions                                                              | 4–13  |

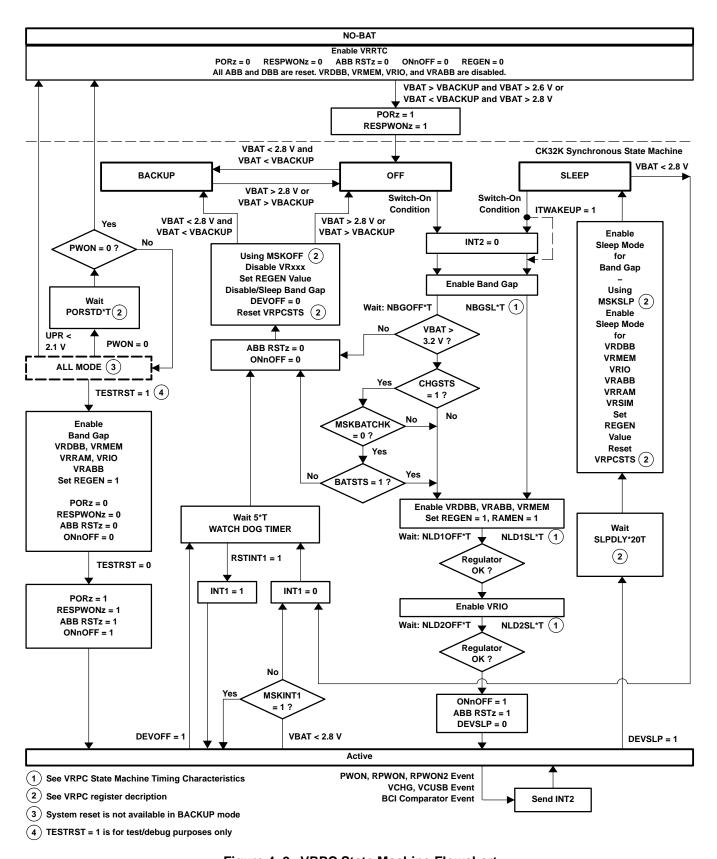

|   |      | 4.6.2      | Definitions                                                                     | 4–14  |

|   |      | 4.6.3      | Power-On Condition                                                              | 4–14  |

|   |      | 4.6.4      | Power-Off Condition                                                             | 4–14  |

|   |      | 4.6.5      | Switch-On Condition                                                             | 4–14  |

|   |      | 4.6.6      | Switch-Off Condition                                                            | 4–15  |

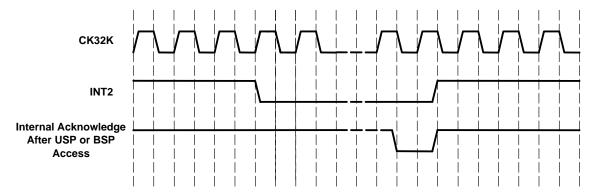

|   |      | 4.6.7      | Interrupt Handling                                                              | 4–15  |

|   |      | 4.6.8      | Debouncing                                                                      | 4–15  |

|   | 4.7  | Automati   | ic Frequency Control                                                            | 4–17  |

|   | 4.8  | Automati   | ic Power Control                                                                | 4–17  |

|   | 4.9  | Auxiliary  | DAC                                                                             | 4–18  |

|   | 4.10 | Backup E   | Battery Charge                                                                  | 4–19  |

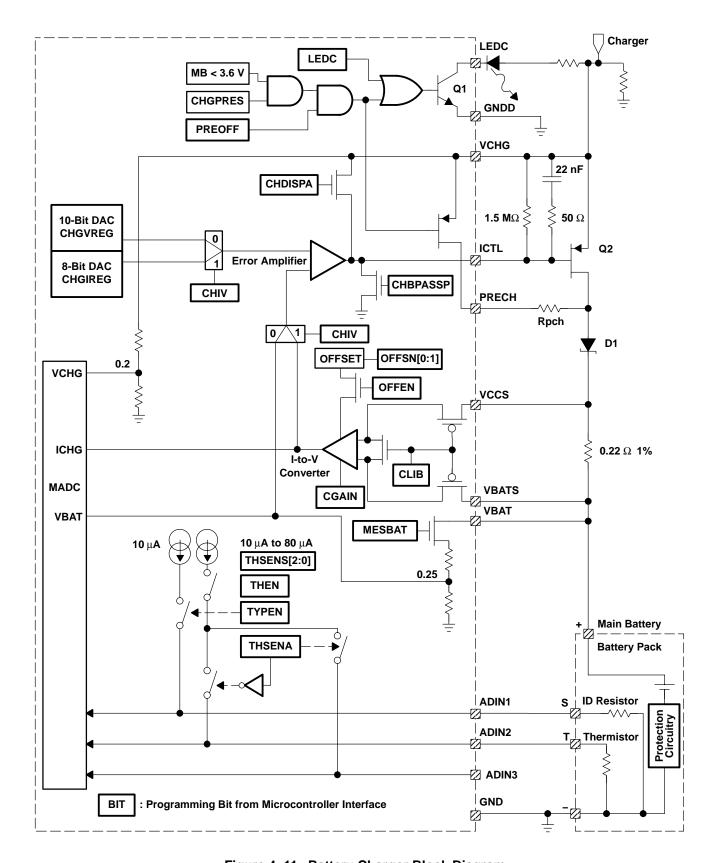

|   | 4.11 | Main Bat   | ttery Charger Interface                                                         | 4–19  |

|   |      | 4.11.1     | Battery Monitoring                                                              | 4–19  |

|   |      | 4.11.2     | Constant Current/Constant Voltage Charging                                      | 4–20  |

|   |      | 4.11.3     | Main Battery Temperature and Main Battery Type                                  |       |

|   |      | _          | Measurements                                                                    | 4–20  |

|   | 4.12 |            | ess Port                                                                        | 4–22  |

|   |      | 4.12.1     | Scan Registers                                                                  | 4–22  |

|   |      | 4.12.2     | Public Instructions                                                             | 4–22  |

| _ |      | 4.12.3     | Boundary Scan                                                                   | 4–23  |

| 5 |      |            | peration                                                                        |       |

|   | 5.1  |            | d Address Format                                                                |       |

|   | 5.2  |            | Register Operations                                                             | . 5–1 |

|   |      | 5.2.1      | Writing to Internal Register (Baseband Serial or                                | - 1   |

|   |      | <b>500</b> | Microcontroller Serial Port)                                                    | . 5–1 |

|   |      | 5.2.2      | Reading From Internal Register (Baseband Serial or Microcontroller Serial Port) | . 5–1 |

|   |      | 5.2.3      | Baseband Burst Operations                                                       | . 5–1 |

|   | 5.3  | Register   | Description                                                                     | . 5–5 |

|   |      | 5.3.1      | Voltage Reference and Power Control (VRPC) Registers                            | 5–5   |

|   |      |            | 5.3.1.1 VRPC Configuration Register                                             |       |

|   |      |            | 5.3.1.2 VRPC Device Mode Register                                               |       |

|   |      |            | 5.3.1.3 VRPC Sleep Mode Mask Register                                           |       |

|   |      |            | 5.3.1.4 VRPC Off Mode Mask Register                                             |       |

|   |      |            | 5.3.1.5 VRPC Status Register                                                    |       |

|   |      |            | 5.3.1.6 VRPC SIM Card and Regulators Control                                    |       |

|   |      |            | Register                                                                        | . 5–9 |

|   |      | 5.3.2      | Monitoring ADC Registers                                                        | . 5–9 |

|   |      |            |                                                                                 |       |

|       | 5.3.2.1     | Monitoring ADC Control Register             | 5–10 |

|-------|-------------|---------------------------------------------|------|

|       | 5.3.2.2     | Monitoring ADC Status Register              | 5–11 |

|       | 5.3.2.3     | Battery Voltage Conversion Register         | 5–11 |

|       | 5.3.2.4     | Battery Voltage Charger Conversion Register | 5–11 |

|       | 5.3.2.5     | Battery Current Charger Conversion Register | 5–12 |

|       | 5.3.2.6     | Backup Battery Voltage Conversion Register  | 5–12 |

|       | 5.3.2.7     | Analog 1 Voltage Conversion Register        | 5–12 |

|       | 5.3.2.8     | Analog 2 Voltage Conversion Register        | 5–13 |

|       | 5.3.2.9     | Analog 3 Voltage Conversion Register        | 5–13 |

|       | 5.3.2.10    | Analog 4 Voltage Conversion Register        | 5–13 |

|       | 5.3.2.11    | Analog 5 Voltage Conversion Register        | 5–14 |

| 5.3.3 | Clock Ger   | nerator (CKG) Registers                     | 5–14 |

|       | 5.3.3.1     | Toggle Bits Register 1                      | 5–14 |

|       | 5.3.3.2     | Toggle Bits Register 2                      | 5–15 |

|       | 5.3.3.3     | Power Down Register                         | 5–16 |

|       | 5.3.3.4     | Test Access Port Control Register           | 5–16 |

|       | 5.3.3.5     | Test Access Port Instruction Register       | 5–17 |

| 5.3.4 | Automatic   | Frequency Control (AFC) Registers           | 5–17 |

|       | 5.3.4.1     | Automatic Frequency Control Register 1      | 5–17 |

|       | 5.3.4.2     | Automatic Frequency Control Register 2      | 5–17 |

|       | 5.3.4.3     | AFC Working Frequency Register              | 5–18 |

|       | 5.3.4.4     | AFC Digital Output Register                 | 5–18 |

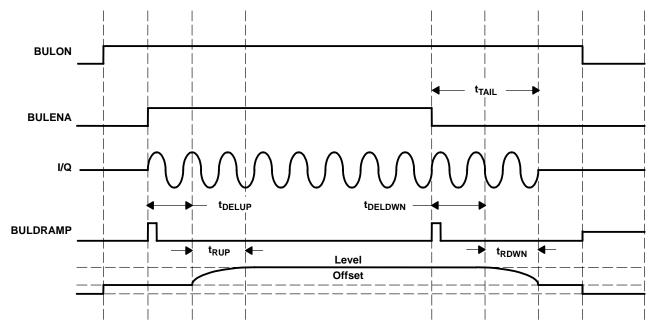

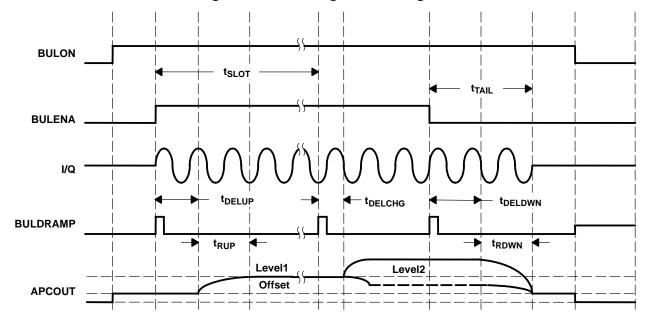

| 5.3.5 | Automatic   | Power Control (APC) Registers               | 5–18 |

|       | 5.3.5.1     | APC Ramp Delay 1 Register                   | 5–19 |

|       | 5.3.5.2     | APC Ramp Delay 2 Register                   | 5–19 |

|       | 5.3.5.3     | Automatic Power Control Register            | 5–19 |

|       | 5.3.5.4     | Automatic Power Control RAM Register        | 5-20 |

|       | 5.3.5.5     | DAC Input Offset and Gain Register          | 5–20 |

|       | 5.3.5.6     | APC Output Register                         | 5–20 |

| 5.3.6 | Auxiliary D | DAC Control Register                        | 5–21 |

| 5.3.7 | Battery Ch  | narger (BCI) Registers                      | 5–21 |

|       | 5.3.7.1     | Main Battery Charging Voltage Register      | 5–21 |

|       | 5.3.7.2     | Main Battery Charging Current Register      | 5–22 |

|       | 5.3.7.3     | Battery Control 1 Register                  | 5-22 |

|       | 5.3.7.4     | Battery Control 2 Register                  | 5-23 |

|       | 5.3.7.5     | Battery Charging Configuration Register     | 5-24 |

|       | 5.3.7.6     | Battery Charger Watchdog Register           | 5-25 |

| 5.3.8 | Interrupt A | And Bus Control Registers (IBIC)            | 5–25 |

|       | 5.3.8.1     | Interrupt Mask Register                     | 5–25 |

|       | 5.3.8.2     | Interrupt Status Register                   | 5–26 |

|       | 5.3.8.3     | Page Select Register                        | 5-26 |

|   |        | 5.3.9     | Baseband      | Codec (BBC) Registers                                  | 5–27  |

|---|--------|-----------|---------------|--------------------------------------------------------|-------|

|   |        |           | 5.3.9.1       | Baseband Uplink I Offset Register                      | 5–27  |

|   |        |           | 5.3.9.2       | Baseband Uplink Q Offset Register                      | 5–27  |

|   |        |           | 5.3.9.3       | Baseband Uplink I DAC Register                         | 5–27  |

|   |        |           | 5.3.9.4       | Baseband Uplink Q DAC Register                         | 5–28  |

|   |        |           | 5.3.9.5       | Baseband Uplink Absolute Gain Calibration Register     | 5–28  |

|   |        |           | 5.3.9.6       | Baseband Uplink Data Buffer 1 Register                 | 5–29  |

|   |        |           | 5.3.9.7       | Baseband Uplink Data Buffer 2 Register                 | 5-30  |

|   |        |           | 5.3.9.8       | Baseband Codec Control Register                        | 5–31  |

|   |        |           | 5.3.9.9       | Baseband Codec Configuration Register                  | 5-32  |

|   |        | 5.3.10    | Voiceband     | Codec Registers (VBC)                                  | 5-33  |

|   |        |           | 5.3.10.1      | Voiceband Control Register 1                           | 5-33  |

|   |        |           | 5.3.10.2      | Voiceband Control Register 2                           | 5-34  |

|   |        |           | 5.3.10.3      | Voiceband Pop Reduction Register                       | 5–35  |

|   |        |           | 5.3.10.4      | Voiceband Uplink Control Register                      | 5-36  |

|   |        |           | 5.3.10.5      | Voiceband Downlink Control Register                    | 5-37  |

|   |        |           | 5.3.10.6      | Audio Control Register                                 | 5-38  |

|   |        |           | 5.3.10.7      | Audio Outputs Control Register                         | 5-39  |

|   |        |           | 5.3.10.8      | Audio Stereo Path Control Register                     | 5-40  |

|   |        |           | 5.3.10.9      | Audio PLL Register                                     | 5-41  |

| 6 | Electr | ical Char | acteristics   |                                                        | . 6–1 |

|   | 6.1    | Absolute  | Maximum I     | Ratings Over Operating Free-Air Temperature            | . 6–1 |

|   | 6.2    | Recomm    | nended Ope    | rating Conditions                                      | . 6–1 |

|   | 6.3    | Electrica | ıl Characteri | stics                                                  | . 6–1 |

|   | 6.4    |           |               | stics Over Recommended Ranges Of Supply r Temperature  | . 6–3 |

|   |        | 6.4.1     |               | egulator RDBB (Under Active Mode)                      |       |

|   |        | 6.4.2     | •             | egulator RDBB (Under Sleep Mode)                       |       |

|   |        | 6.4.3     | Voltage Re    | egulator RIO (Under Active Mode)                       | . 6–4 |

|   |        | 6.4.4     | •             | egulator RIO (Under Sleep Mode)                        |       |

|   |        | 6.4.5     | Voltage Re    | egulator RRAM (Under Active Mode)                      | . 6–4 |

|   |        | 6.4.6     | Voltage Re    | egulator RRAM (Under Sleep Mode)                       | . 6–5 |

|   |        | 6.4.7     | Voltage Re    | egulator RRAM Reverse Leakage Current (Under Off Mode) |       |

|   |        | 6.4.8     |               | egulator RMEM (Únder Active Mode)                      |       |

|   |        | 6.4.9     | Voltage Re    | egulator RMEM (Under Sleep Mode)                       | . 6–5 |

|   |        | 6.4.10    | Voltage Re    | egulator RSIM (Under Active Mode)                      | . 6–6 |

|   |        | 6.4.11    | Voltage Re    | egulator RSIM (Under Sleep Mode)                       | . 6–6 |

|   |        | 6.4.12    | •             | egulator RABB (Under Active Mode)                      |       |

|   |        | 6.4.13    | •             | egulator RABB (Under Sleep Mode)                       |       |

|   |        | 6.4.14    | Voltage Re    | egulator RRTC                                          | . 6–7 |

|   |        | 6.4.15    | Voltage Re    | egulator RUSB                                          | . 6–7 |

|   |        | 6.4.16    | Bandgap F     | Reference                                              | . 6–8 |

|   |        |           |               |                                                        |       |

| 6.5  | VRPC S   | State Machine Characteristics                      | . 6–8 |

|------|----------|----------------------------------------------------|-------|

|      | 6.5.1    | Timing Characteristics                             | . 6–8 |

|      | 6.5.2    | Power On/Power Off and Backup Conditions           | . 6–8 |

|      | 6.5.3    | Switch On Conditions/Accessories Plugged/Unplugged |       |

|      |          | Interrupt Threshold                                |       |

| 6.6  |          | Consumption                                        |       |

|      | 6.6.1    | Device Off Modes                                   |       |

|      | 6.6.2    | Device On Modes                                    |       |

|      | 6.6.3    | Blocks Power Consumption                           | . 6–9 |

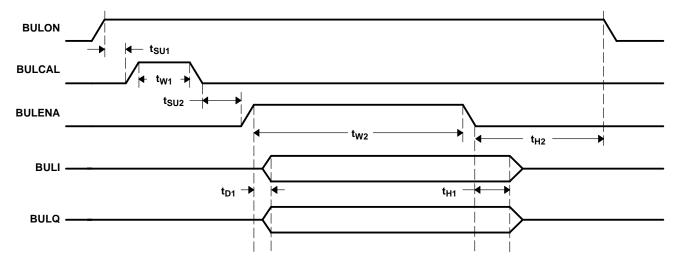

| 6.7  |          | rd Interface Switching Characteristics             |       |

| 6.8  | Battery  | Charger Interface                                  | 6–10  |

|      | 6.8.1    | Backup Battery Charger                             | 6–10  |

|      | 6.8.2    | Main Battery Charger                               | 6–11  |

|      | 6.8.3    | BCI Protection Comparator                          | 6–12  |

|      | 6.8.4    | BCI LED Driver                                     | 6–12  |

|      | 6.8.5    | BCI Watchdog Timer                                 | 6–12  |

| 6.9  | ADC Ch   | naracteristics                                     | 6–12  |

|      | 6.9.1    | Electrical Characteristics                         | 6–12  |

|      | 6.9.2    | Switching Characteristics                          | 6–12  |

|      | 6.9.3    | Global Characteristics                             | 6–12  |

| 6.10 | Automa   | tic Power Control (APC)                            | 6–13  |

|      | 6.10.1   | DAC 10 Characteristics                             | 6–13  |

|      | 6.10.2   | Output Stage Characteristics                       | 6–13  |

|      | 6.10.3   | Timings                                            | 6–13  |

| 6.11 | Clocks A | And Interrupts                                     | 6–15  |

| 6.12 | USP Int  | erface Timings Requirements                        | 6–15  |

| 6.13 | TSP Inte | erface Timings Requirements                        | 6–16  |

| 6.14 | VSP Inte | erface Timings Requirements                        | 6–17  |

| 6.15 | Audio In | nterface Timings Requirements                      | 6–18  |

| 6.16 | BSP Inte | erface Timings Requirements                        | 6–19  |

| 6.17 | JTAG In  | Iterface Timings Requirements                      | 6–20  |

| 6.18 | Operatir | ng Characteristics                                 | 6–21  |

|      | 6.18.1   | Audio Codec                                        | 6–21  |

|      |          | 6.18.1.1 Audio Inputs                              | 6-21  |

|      |          | 6.18.1.2 Voiceband: Uplink Path                    | 6-22  |

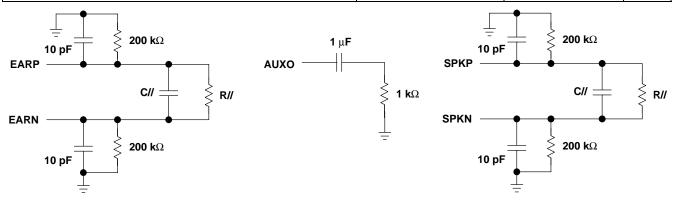

|      |          | 6.18.1.3 Audio Outputs                             | 6-24  |

|      |          | 6.18.1.4 Voiceband: Downlink Path                  | 6-25  |

|      |          | 6.18.1.5 Audio Stereo Path                         | 6–28  |

|      | 6.18.2   | Baseband Uplink General Characteristics            | 6-29  |

|      |          | 6.18.2.1 Baseband Uplink Path                      | 6-29  |

|      |          | 6.18.2.2 Baseband Downlink Path                    | 6-31  |

|      | 6.18.3   | Auxiliary DAC                                      | 6-33  |

|      |          | 6.18.3.1 10-Bit DAC Characteristics                | 6-33  |

|      | 6.18.4   | Automatic Frequency Control                        | 6-33  |

| 7 | Mecha | anical Information |                         | . 7–1 |

|---|-------|--------------------|-------------------------|-------|

|   | 6.19  | ESD Performance    |                         | 6–34  |

|   |       | 6.18.4.2           | AFC Output Stage        | 6–34  |

|   |       | 6.18.4.1           | AFC DAC Characteristics | 6–33  |

# **List of Illustrations**

| Figure | Title                                    | Page |

|--------|------------------------------------------|------|

| 2–1    | TWL3016 GQW Package Terminal Assignments | 2–2  |

| 3–1    | TWL3016 Functional Block Diagram         | 3–2  |

| 4–1    | Audio Codec Block Diagram                | 4–2  |

| 4–2    | Voice Uplink Path                        | 4–4  |

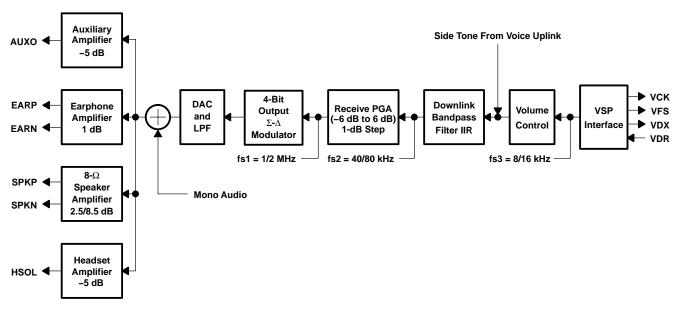

| 4–3    | Voice Codec Downlink Path                | 4–5  |

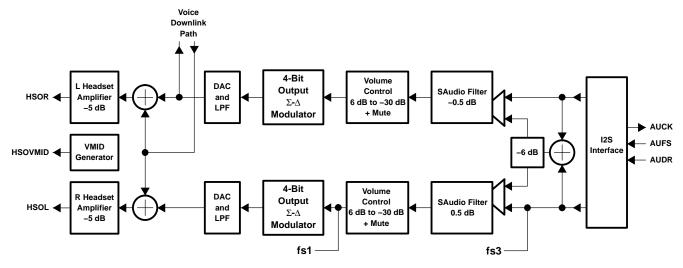

| 4–4    | Stereo Audio Path                        | 4–6  |

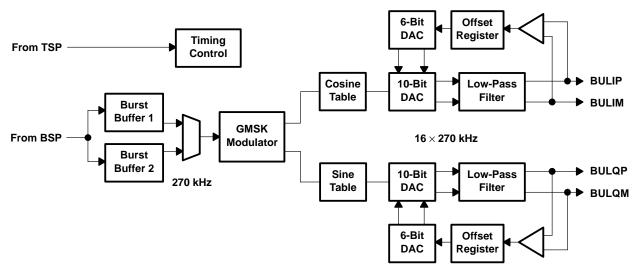

| 4–5    | Baseband Uplink Block Diagram            | 4–8  |

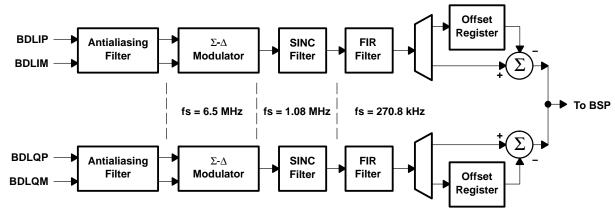

| 4–6    | Baseband Downlink Block Diagram          | 4–9  |

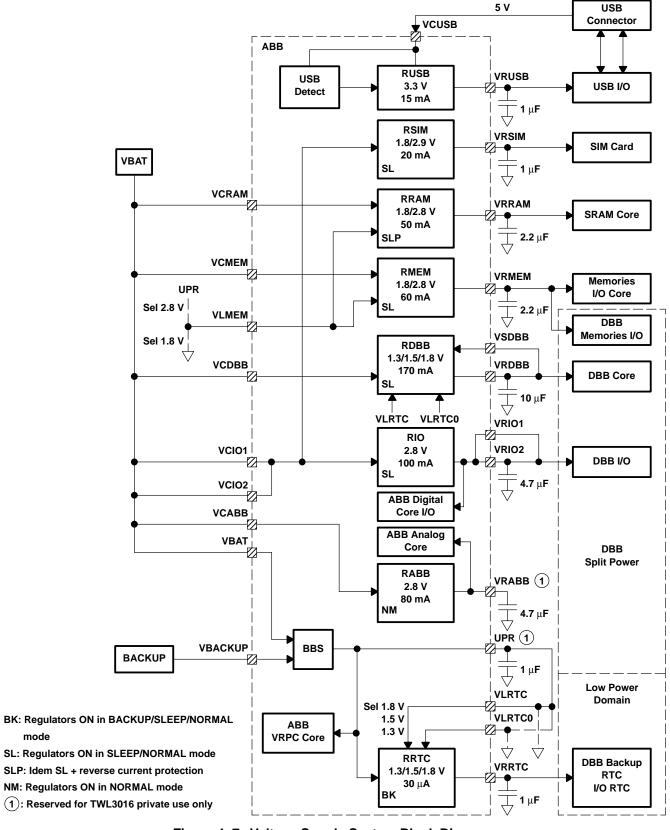

| 4–7    | Voltage Supply System Block Diagram      | 4–11 |

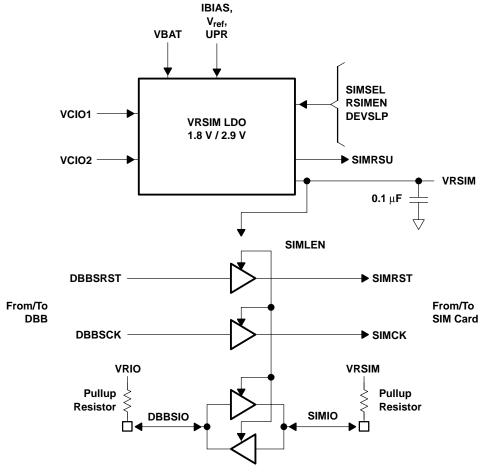

| 4–8    | SIM Interface Block Diagram              | 4–12 |

| 4–9    | VRPC State Machine Flowchart             | 4–16 |

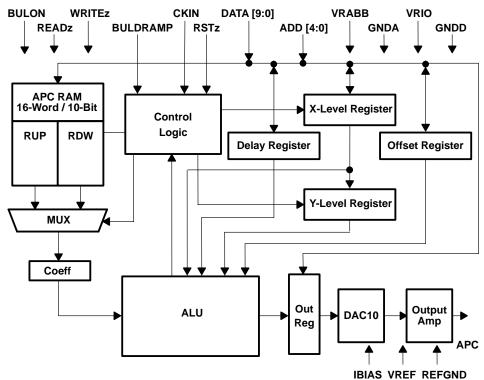

| 4–10   | APC Block Diagram                        | 4–18 |

| 4–11   | Battery Charger Block Diagram            | 4–21 |

| 6–1    | APC Single Slot Timing                   | 6–14 |

| 6–2    | APC Multislot Timing                     | 6–14 |

| 6–3    | Interrupt 2 Timing                       | 6–15 |

| 6–4    | Receive and Transmit USP Operations      | 6–15 |

| 6–5    | TSP Interface Timing Diagram             | 6–16 |

| 6–6    | Voice Serial Port Operations             | 6–17 |

| 6–7    | I2S Audio Serial Port Operations         | 6–18 |

| 6–8    | Stereo Audio PLL External Filter         | 6–18 |

| 6–9    | Single BSP Operations                    | 6–19 |

| 6–10   | Adjacent BSP Operations                  | 6–20 |

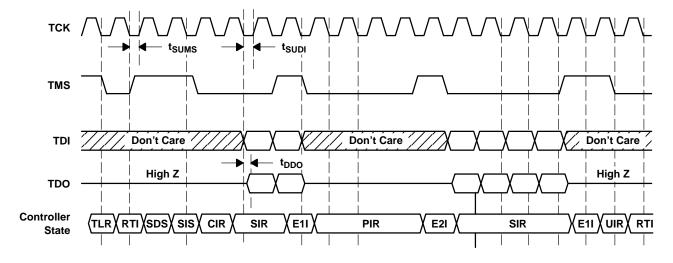

| 6–11   | Controller State                         | 6–20 |

| 6–12   | Audio Output Loading                     | 6–24 |

| 6–13   | 1 3                                      |      |

| 6–14   | Baseband Uplink Timing                   | 6–30 |

| 6–15   | GSMK Multislot Modulation Timing Scheme  | 6–31 |

| 6–16   | Baseband Downlink Timing                 | 6–33 |

# **List of Tables**

| Table | Title                                                       | Page |

|-------|-------------------------------------------------------------|------|

| 2–1   | Signal Names Sorted by GQW Terminal Number                  | 2–3  |

| 2–2   | Signal Names Sorted Alphanumerically to GQW Terminal Number | 2–4  |

| 2-3   | Terminal Functions                                          | 2–5  |

| 4–1   | Audio Codec Output Signals                                  | 4–3  |

| 4–2   | Tel PLL                                                     | 4–6  |

| 4–3   | Stereo Audio PLL                                            | 4–6  |

| 5–1   | Register Cross Reference Listing                            | 5–2  |

| 5–2   | Register Map                                                | 5–3  |

| 5–3   | VRPC Configuration Register Description                     | 5–5  |

| 5–4   | VPRC Device Mode Register Description                       | 5–5  |

| 5–5   | VRPC Mask Register Description                              | 5–6  |

| 5–6   | VRPC Mask VRABB Register Description                        | 5–7  |

| 5–7   | VRPC Status Register Description                            | 5–8  |

| 5–8   | SIM Card and Regulators Control Register Description        | 5–9  |

| 5–9   | Monitoring ADC Control Register Description                 | 5–10 |

| 5–10  | Monitoring ADC Status Register Description                  | 5–11 |

| 5–11  | Battery Voltage Conversion Register Description             | 5–11 |

| 5–12  | Battery Voltage Charger Conversion Register Description     | 5–11 |

| 5–13  | Battery Current Charger Conversion Register Description     | 5–12 |

| 5–14  | Backup Battery Voltage Conversion Register Description      | 5–12 |

| 5–15  | Analog 1 Voltage Conversion Register Description            | 5–12 |

| 5–16  | Analog 2 Voltage Conversion Register Description            | 5–13 |

| 5–17  | Analog 3 Voltage Conversion Register Description            | 5–13 |

| 5–18  | Analog 4 Voltage Conversion Register Description            | 5–13 |

| 5–19  | Analog 5 Voltage Conversion Register Description            | 5–14 |

| 5–20  | Toggle Bits Register 1 Description                          | 5–14 |

| 5–21  | Toggle Bits Register 2 Description                          | 5–15 |

| 5–22  | Power Down Register Description                             | 5–16 |

| 5–23  | Test Access Port Control Register Description               | 5–16 |

| 5–24  | Test Access Port Instruction Register Description           | 5–17 |

| 5–25  | Automatic Frequency Control Register 1 Description          | 5–17 |

| 5-26  | Automatic Frequency Control Register 2 Description          | 5–17 |

| 5-27  | AFC Working Frequency Register Description                  | 5–18 |

| 5–28  | AFC Digital Output Register Description                     | 5–18 |

| 5-29  | APC Ramp Delay 1 Register Description                       | 5–19 |

| 5-30  | APC Ramp Delay 2 Register Description                       | 5–19 |

| 5-31  | Automatic Power Control Register Description                | 5–19 |

| 5–32 | Offset DAC Input Register Description                          | 5–20 |

|------|----------------------------------------------------------------|------|

| 5–33 | APC Output Register Description                                | 5–20 |

| 5–34 | Auxiliary DAC Control Register Description                     | 5–21 |

| 5–35 | Main Battery Charging Voltage Register Description             | 5–21 |

| 5–36 | Main Battery Charging Current Register Description             | 5–22 |

| 5–37 | Battery Control 1 Register Description                         | 5–22 |

| 5–38 | Battery Control 2 Register Description                         | 5-23 |

| 5–39 | Battery Charging Configuration Register Description            | 5–24 |

| 5–40 | Battery Charging Configuration Register Description            | 5–25 |

| 5–41 | Interrupt Mask Register Description                            | 5–25 |

| 5–42 | Interrupt Status Register Description                          | 5-26 |

| 5–43 | Page Select Register Description                               | 5-26 |

| 5–44 | Baseband Uplink I Offset Register Description                  | 5–27 |

| 5–45 | Baseband Uplink Q Offset Register Description                  | 5–27 |

| 5–46 | Baseband Uplink I DAC Register Description                     | 5–27 |

| 5–47 | Baseband Uplink Q DAC Register Description                     | 5–28 |

| 5–48 | Baseband Uplink Absolute Gain Calibration Register Description | 5–28 |

| 5–49 | Baseband Uplink Data Buffer 1 Register Description             | 5–29 |

| 5–50 | Baseband Uplink Data Buffer 2 Register Description             | 5-30 |

| 5–51 | Baseband Codec Control Register Description                    | 5–31 |

| 5–52 | Baseband Configuration Register Description                    | 5–32 |

| 5–53 | Voiceband Control Register 1 Description                       | 5–33 |

| 5–54 | Voiceband Control Register 2 Description                       | 5–34 |

| 5–55 | Voiceband Pop Reduction Register Description                   | 5–35 |

| 5–56 | Voiceband Uplink Control Register Description                  | 5–36 |

| 5–57 | Voiceband Downlink Control Register Description                | 5–37 |

| 5–58 | Audio Control Register Description                             | 5–38 |

| 5–59 | Audio Outputs Control Register Description                     | 5–39 |

| 5–60 | Audio Stereo Path Control Register Description                 |      |

| 5–61 | Audio Stereo Path Control Register Description                 | 5-41 |

#### 1 Introduction

This chapter provides an overview of the Texas Instruments TWL3016 device and its features.

#### 1.1 Description

The TWL3016 device is an analog baseband (ABB) device which, together with a digital baseband (DBB) device, is part of a TI TMS320™ DSP (digital signal processor) solution intended for digital cellular telephone applications including the GSM 900, DCS 1800, and PCS 1900 standards (dual-band capability).

The TWL3016 device includes a complete set of baseband functions that perform the interfacing and processing of voice signals, the baseband in-phase (I) and quadrature (Q) signals which support both the single-slot and multislot modes, and MS Class 12 for GMSK modulation types (3GPP TS 05.02). The TWL3016 device also includes associated auxiliary RF control features, supply voltage regulation, battery charging controls, and switch on/off system analysis.

The TWL3016 device interfaces with the DBB device through a digital baseband serial port (BSP) and a voiceband serial port (VSP). The signal ports communicate with a DSP core (LEAD). A microcontroller serial port (USP) communicates with the microcontroller core and a time serial port (TSP) communicates with the time processing unit (TPU) for real-time control.

A specific module is dedicated to support the 1.8-V/3-V SIM card interface. The module includes the generation of the SIM card supply voltage, as well as level shifters to adapt the SIM card signal levels to the microcontroller I/O signal levels. The TWL3016 device meets JTAG testability standard (IEEE Std 1131.1 – 1990) through a standard test access port (TAP) and boundary scan.

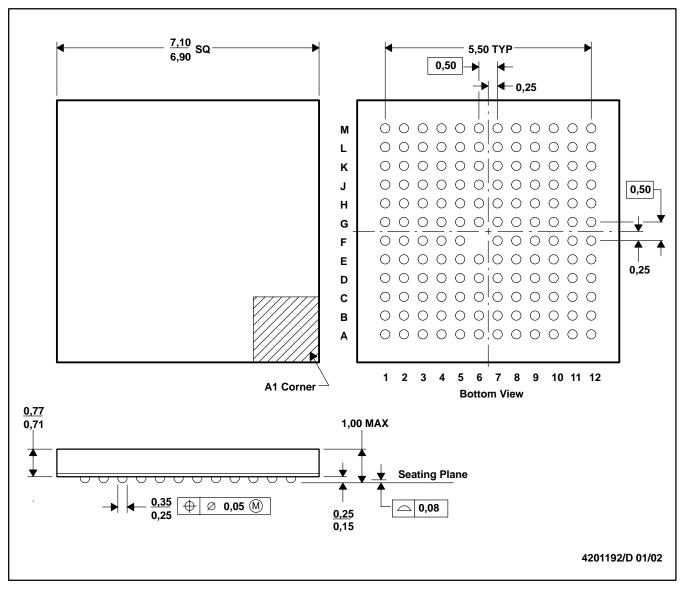

The TW3016 device also includes an on-chip voltage reference, under-voltage detection, and power-on reset circuits. The TWL3016 device is packaged in Texas Instruments 143-terminal, 0,5-mm pitch, MicroStarJunior™ ball grid array (GQW).

#### 1.2 Features

The TWL3016 device supports the following features:

- Applications include the GSM 900, PCS 1900, and DSC 1800 cellular telephones

- Baseband coder/decoder (codec) single- and multislot with I/Q RF interface

- Auxiliary RF converters

- Five-channel analog-to-digital converter (ADC)

- Six low-dropout (LDO), linear voltage regulators targeted for core, general I/O, memory I/O, SIM I/O, with low guiescent current mode

- LDO voltage regulators dedicated to the USB interface

- High voltage (20 V) Li-Ion or Ni-MH battery charging control

- Voltage detectors (with power-off delay)

- Dedicated very low quiescent current supply domain

- Voice codec

- 13.5-bit linear codec

- Differential input MIC AMP

- Two single input AUXI/HSMIC AMP

- Bias amplifier for MIC/HSMIC

- Differential output earphone driver

- Differential output speaker driver (8-Ω load)

- Single output AUXO

- Audio DAC based on I2S format

- 16-bit linear DAC

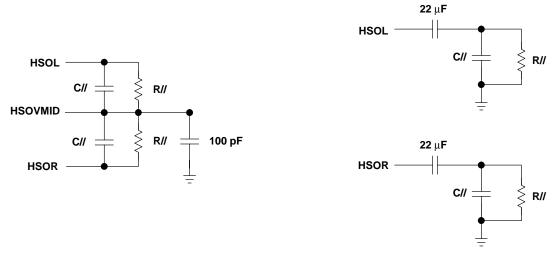

- Stereo headphone drivers with pseudoground to eliminate external capacitors (32-Ω load)

- Soft volume change/mute features

- 143-terminal MicroStarJunior™ BGA

#### 1.3 Trademarks

MicroStar Junior BGA is a trademark of Texas Instruments.

TMS320 DSP is a trademark of Texas Instruments.

Other trademarks are the property of their respective owners.

#### 1.4 Ordering Information

| ORDERING NUMBER | VOLTAGE       | T <sub>A</sub> |

|-----------------|---------------|----------------|

| TWL3016B1GQW    | -0.3 V to 7 V | −30°C to 85°C  |

# **2 Terminal Descriptions**

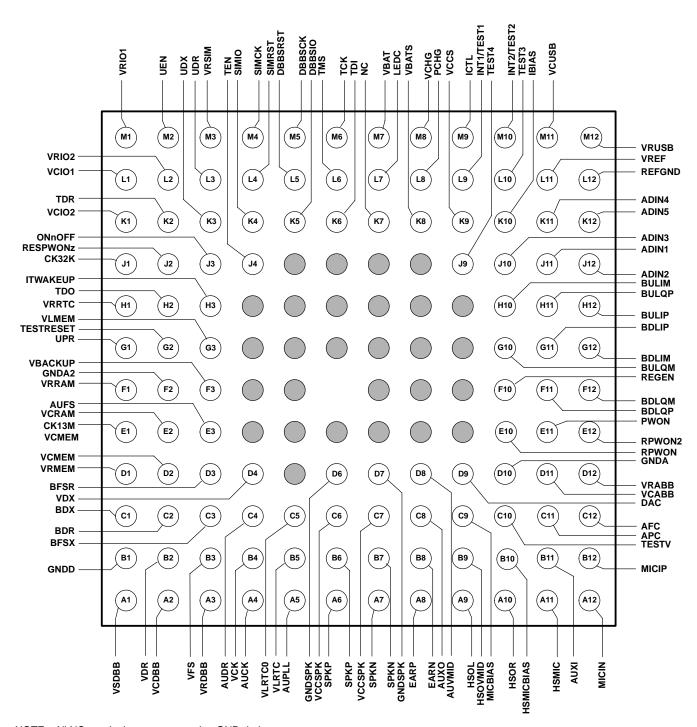

This section provides the terminal descriptions for the TWL3016 device. Figure 2–1 shows the signal assigned to each terminal in the package. Table 2–1 and Table 2–2 provide a cross-reference between each terminal number and the signal name on that terminal. Table 2–1 is arranged in terminal number order, and Table 2–2 lists the signals in alphabetical order.

# GQW PACKAGE (BOTTOM VIEW)

NOTE: All NC terminals are connected to GND during test.

Figure 2-1. TWL3016 GQW Package Terminal Assignments

Table 2–1. Signal Names Sorted by GQW Terminal Number

| NUMBER | SIGNAL NAME |

|--------|-------------|--------|-------------|--------|-------------|--------|-------------|

| A1     | VSDBB       | D1     | VRMEM       | G1     | UPR         | K1     | VCIO2       |

| A2     | VCDBB       | D2     | VCMEM       | G2     | TESTRESET   | K2     | TDR         |

| А3     | VRDBB       | D3     | BFSR        | G3     | VLMEM       | K3     | UDX         |

| A4     | AUCK        | D4     | VDX         | G4     | GND         | K4     | SIMIO       |

| A5     | AUPLL       | D5     | GND         | G5     | GND         | K5     | DBBSIO      |

| A6     | SPKP        | D6     | GNDSPK      | G6     | GND         | K6     | TDI         |

| A7     | SPKN        | D7     | GNDSPK      | G7     | GND         | K7     | NC          |

| A8     | EARP        | D8     | AUVMID      | G8     | GND         | K8     | VBATS       |

| A9     | HSOL        | D9     | DAC         | G9     | GND         | K9     | VCCS        |

| A10    | HSOR        | D10    | GNDA        | G10    | BULQM       | K10    | IBIAS       |

| A11    | HSMICP      | D11    | VCABB       | G11    | BDLIP       | K11    | ADIN4       |

| A12    | MICIN       | D12    | VRABB       | G12    | BDLIM       | K12    | ADIN5       |

| B1     | GNDD        | E1     | CK13M       | H1     | VRRTC       | L1     | VCIO1       |

| B2     | VDR         | E2     | VCRAM       | H2     | TDO         | L2     | VRIO2       |

| В3     | VFS         | E3     | AUFS        | H3     | ITWAKEUP    | L3     | UDR         |

| B4     | VCK         | E4     | GND         | H4     | GND         | L4     | SIMRST      |

| B5     | VLRTC       | E5     | GND         | H5     | GND         | L5     | DBBSRST     |

| B6     | SPKP        | E6     | GND         | H6     | GND         | L6     | TMS         |

| B7     | SPKN        | E7     | GND         | H7     | GND         | L7     | LEDC        |

| B8     | EARN        | E8     | GND         | H8     | GND         | L8     | PCHG        |

| B9     | HSOVMID     | E9     | GND         | H9     | GND         | L9     | INT1/TEST1  |

| B10    | HSMICBIAS   | E10    | RPWON       | H10    | BULIM       | L10    | TEST3       |

| B11    | AUXI        | E11    | PWON        | H11    | BULQP       | L11    | VREF        |

| B12    | MICIP       | E12    | RPWON2      | H12    | BULIP       | L12    | REFGND      |

| C1     | BDX         | F1     | VRRAM       | J1     | CK32K       | M1     | VRIO1       |

| C2     | BDR         | F2     | GNDA2       | J2     | RESPWONz    | M2     | UEN         |

| C3     | BFSX        | F3     | VBACKUP     | J3     | ON_nOFF     | М3     | VRSIM       |

| C4     | AUDR        | F4     | GND         | J4     | TEN         | M4     | SIMCK       |

| C5     | VLRTC0      | F5     | GND         | J5     | GND         | M5     | DBBSCK      |

| C6     | VCCSPK      |        |             | J6     | GND         | M6     | TCK         |

| C7     | VCCSPK      | F7     | GND         | J7     | GND         | M7     | VBAT        |

| C8     | AUXO        | F8     | GND         | J8     | GND         | M8     | VCHG        |

| C9     | MICBIAS     | F9     | GND         | J9     | TEST4       | M9     | ICTL        |

| C10    | TESTV       | F10    | REGEN       | J10    | ADIN3       | M10    | INT2/TEST2  |

| C11    | APC         | F11    | BDLQP       | J11    | ADIN1       | M11    | VCUSB       |

| C12    | AFC         | F12    | BDLQM       | J12    | ADIN2       | M12    | VRUSB       |

Table 2–2. Signal Names Sorted Alphanumerically to GQW Terminal Number

| SIGNAL NAME | NUMBER | SIGNAL NAME | NUMBER | SIGNAL NAME | NUMBER | SIGNAL NAME | NUMBER |

|-------------|--------|-------------|--------|-------------|--------|-------------|--------|

| ADIN1       | J11    | GND         | E5     | IBIAS       | K10    | UDX         | K3     |

| ADIN2       | J12    | GND         | E6     | ICTL        | M9     | UEN         | M2     |

| ADIN3       | J10    | GND         | E7     | INT1/TEST1  | L9     | UPR         | G1     |

| ADIN4       | K11    | GND         | E8     | INT2/TEST2  | M10    | VBACKUP     | F3     |

| ADIN5       | K12    | GND         | E9     | ITWAKEUP    | H3     | VBAT        | M7     |

| AFC         | C12    | GND         | F4     | LEDC        | L7     | VBATS       | K8     |

| APC         | C11    | GND         | F5     | MICBIAS     | C9     | VCABB       | D11    |

| AUCK        | A4     | GND         | F7     | MICIN       | A12    | VCCS        | K9     |

| AUDR        | C4     | GND         | F8     | MICIP       | B12    | VCCSPK      | C6     |

| AUFS        | E3     | GND         | F9     | NC          | K7     | VCCSPK      | C7     |

| AUPLL       | A5     | GND         | G4     | ON_nOFF     | J3     | VCDBB       | A2     |

| AUVMID      | D8     | GND         | G5     | PCHG        | L8     | VCHG        | M8     |

| AUXI        | B11    | GND         | G6     | PWON        | E11    | VCIO1       | L1     |

| AUXO        | C8     | GND         | G7     | REFGND      | L12    | VCIO2       | K1     |

| BDLIM       | G12    | GND         | G8     | REGEN       | F10    | VCK         | B4     |

| BDLIP       | G11    | GND         | G9     | RESPWONz    | J2     | VCMEM       | D2     |

| BDLQM       | F12    | GND         | H4     | RPWON       | E10    | VCRAM       | E2     |

| BDLQP       | F11    | GND         | H5     | RPWON2      | E12    | VCUSB       | M11    |

| BDR         | C2     | GND         | H6     | SIMCK       | M4     | VDR         | B2     |

| BDX         | C1     | GND         | H7     | SIMIO       | K4     | VDX         | D4     |

| BFSR        | D3     | GND         | H8     | SIMRST      | L4     | VFS         | В3     |

| BFSX        | C3     | GND         | H9     | SPKN        | A7     | VLMEM       | G3     |

| BULIM       | H10    | GND         | J5     | SPKN        | B7     | VLRTC       | B5     |

| BULIP       | H12    | GND         | J6     | SPKP        | A6     | VLRTC0      | C5     |

| BULQM       | G10    | GND         | J7     | SPKP        | В6     | VRABB       | D12    |

| BULQP       | H11    | GND         | J8     | TCK         | M6     | VRDBB       | А3     |

| CK13M       | E1     | GNDA        | D10    | TDI         | K6     | VREF        | L11    |

| CK32K       | J1     | GNDA2       | F2     | TDO         | H2     | VRIO1       | M1     |

| DAC         | D9     | GNDD        | B1     | TDR         | K2     | VRIO2       | L2     |

| DBBSCK      | M5     | GNDSPK      | D6     | TEN         | J4     | VRMEM       | D1     |

| DBBSIO      | K5     | GNDSPK      | D7     | TESTRESET   | G2     | VRRAM       | F1     |

| DBBSRST     | L5     | HSMICBIAS   | B10    | TESTV       | C10    | VRRTC       | H1     |

| EARN        | B8     | HSMICP      | A11    | TEST3       | L10    | VRSIM       | M3     |

| EARP        | A8     | HSOL        | A9     | TEST4       | J9     | VRUSB       | M12    |

| GND         | D5     | HSOR        | A10    | TMS         | L6     | VSDBB       | A1     |

| GND         | E4     | HSOVMID     | В9     | UDR         | L3     |             |        |

Table 2–3 shows the terminal functions for the TWL3016 device.

Table 2-3. Terminal Functions

| TERMINAL  |        |              |     |                                                               |                    |  |

|-----------|--------|--------------|-----|---------------------------------------------------------------|--------------------|--|

| NAME      | NUMBER | SUPPLIES     | 1/0 | DESCRIPTION                                                   | COMMENTS           |  |

| ADIN1     | J11    | VRABB/GNDA   | I/O | Monitoring ADC input 1 and battery type current source        |                    |  |

| ADIN2     | J12    | VRABB/GNDA   | I/O | Monitoring ADC input 2 and battery temperature current source |                    |  |

| ADIN3     | J10    | VRABB/GNDA   | ı   | Monitoring ADC input 3 and battery temperature current source |                    |  |

| ADIN4     | K11    | VRABB/GNDA   | I   | Monitoring ADC input 4 (spare)                                |                    |  |

| ADIN5     | K12    | VRABB/GNDA   | ı   | Monitoring ADC input 5 (spare)                                |                    |  |

| AFC       | C12    | VRABB/GNDA   | 0   | Automatic frequency control DAC output                        | External capacitor |  |

| APC       | C11    | VRABB/GNDA   | 0   | Automatic power control DAC output                            |                    |  |

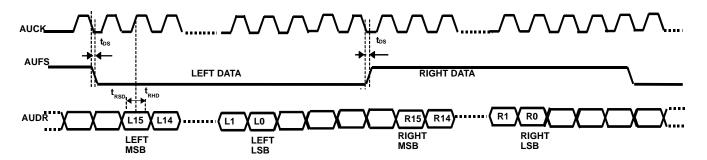

| AUCK      | A4     | VRIO/GNDD    | 0   | I2S serial port clock                                         |                    |  |

| AUDR      | C4     | VRIO/GNDD    | I   | I2S serial port receive data                                  |                    |  |

| AUFS      | E3     | VRIO/GNDD    | 0   | I2S serial port frame synchronization                         |                    |  |

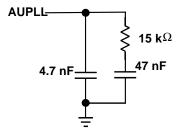

| AUPLL     | A5     | VRABB/GNDA   | I/O | Audio PLL filter                                              | External capacitor |  |

| AUVMID    | D8     | VRABB/GNDA   | I/O | Audio VMID filter                                             | External capacitor |  |

| AUXI      | B11    | VRABB/REFGND | ı   | Auxiliary speech signal input                                 |                    |  |

| AUXO      | C8     | VRABB/GNDA   | 0   | Auxiliary speech signal output                                |                    |  |

| BDLIM     | G12    | VRABB/GNDA   | ı   | In-phase input (I–) baseband codec downlink                   |                    |  |

| BDLIP     | G11    | VRABB/GNDA   | ı   | In-phase input (I+) baseband codec downlink                   |                    |  |

| BDLQM     | F12    | VRABB/GNDA   | ı   | Quadrature input (Q-) baseband codec downlink                 |                    |  |

| BDLQP     | F11    | VRABB/GNDA   | ı   | Quadrature input (Q+) baseband codec downlink                 |                    |  |

| BDR       | C2     | VRIO/GNDD    | ı   | Baseband serial port receive data                             |                    |  |

| BDX       | C1     | VRIO/GNDD    | 0   | Baseband serial port transmit data                            |                    |  |

| BFSR      | D3     | VRIO/GNDD    | ı   | Baseband serial port receive frame synchronization            |                    |  |

| BFSX      | C3     | VRIO/GNDD    | 0   | Baseband serial port transmit frame synchronization           |                    |  |

| BULIM     | H10    | VRABB/GNDA   | 0   | In-phase output (I–) baseband codec uplink                    |                    |  |

| BULIP     | H12    | VRABB/GNDA   | 0   | In-phase output (I+) baseband codec uplink                    |                    |  |

| BULQM     | G10    | VRABB/GNDA   | 0   | Quadrature output (Q-) baseband codec uplink                  |                    |  |

| BULQP     | H11    | VRABB/GNDA   | 0   | Quadrature output (Q+) baseband codec uplink                  |                    |  |

| CK13M     | E1     | VRIO/GNDD    | I   | 13-MHz master clock input and BSP/TSP/USP clock               |                    |  |

| CK32K     | J1     | VRRTC/GNDD   | I   | 32-kHz clock input                                            |                    |  |

| DAC       | D9     | VRABB/GNDA   | 0   | Auxiliary 10-bit DAC output                                   |                    |  |

| DBBSCK    | M5     | VRIO/GNDD    | I   | SIM card shifters clock input                                 |                    |  |

| DBBSIO    | K5     | VRIO/GNDD    | I/O | SIM card shifters data                                        | External pullup    |  |

| DBBSRST   | L5     | VRIO/GNDD    | ı   | SIM card shifters reset input                                 |                    |  |

| EARN      | B8     | VRABB/GNDA   | 0   | Earphone amplifier output (–)                                 |                    |  |

| EARP      | A8     | VRABB/GNDA   | 0   | Earphone amplifier output (+)                                 |                    |  |

| GNDA      | D10    | GNDA         | I/O | Power ground return for VRABB                                 |                    |  |

| GNDA2     | F2     | GNDA2        | I/O | Power ground return for VBAT and VCHG                         |                    |  |

| GNDD      | B1     | GNDD         | I/O | Power ground return for VRIO/UPR                              |                    |  |

| GNDSPK    | D6     | GNDSPK       | I/O | 8- $\Omega$ speaker amplifier ground                          |                    |  |

| GNDSPK    | D7     | GNDSPK       | I/O | $8-\Omega$ speaker amplifier ground                           |                    |  |

| HSMICBIAS | B10    | VRABB/REFGND | 0   | Head set microphone bias supply                               |                    |  |

Table 2–3. Terminal Functions (Continued)

| TERMINAL   |        |               |     |                                                        |                    |  |

|------------|--------|---------------|-----|--------------------------------------------------------|--------------------|--|

| NAME       | NUMBER | SUPPLIES      | I/O | DESCRIPTION                                            | COMMENTS           |  |

| HSMICP     | A11    | VRABB/REFGND  | I   | Head set microphone amplifier input                    |                    |  |

| HSOL       | A9     | VRABB/REFGND  | 0   | Head set 32-Ω driver (single ended)                    |                    |  |

| HSOR       | A10    | VRABB/REFGND  | 0   | Head set 32-Ω driver (single ended)                    |                    |  |

| HSOVMID    | B9     | VRABB/REFGND  | 0   | Head set 32-Ω bias supply                              |                    |  |

| IBIAS      | K10    | VRABB/REFGND  | I/O | Bias current reference resistor (120 kΩ)               | External resistor  |  |

| ICTL       | M9     | VCHG/GNDA2    | 0   | Charger external transistor control                    |                    |  |

| INT1/TEST1 | L9     | VRIO/GNDD     | I/O | Fast interrupt/test pad 1 (default is INT1)            |                    |  |

| INT2/TEST2 | M10    | VRIO/GNDD     | I/O | Microcontroller interrupt/test pad 2 (default is INT2) |                    |  |

| ITWAKEUP   | H3     | VRRTC/GNDD    | I   | Real-time wake-up input                                |                    |  |

| LEDC       | L7     | VCHG/GNDA2    | I   | LED driver: charging device indicator                  |                    |  |

| MICBIAS    | C9     | VRABB/REFGND  | 0   | Microphone bias supply                                 |                    |  |

| MICIN      | A12    | VRABB/REFGND  | I   | Microphone amplifier input (-)                         |                    |  |

| MICIP      | B12    | VRABB/REFGND  | I   | Microphone amplifier input (+)                         |                    |  |

| ONnOFF     | J3     | VRRTC/GNDD    | 0   | Digital baseband reset (at each switch on)             |                    |  |

| PCHG       | L8     | VCHG/GNDA2    | 0   | Battery precharge output current                       |                    |  |

| PWON       | E11    | VBAT/GNDD     | I   | On button input                                        | Pullup             |  |

| REFGND     | L12    | REFGND        | I/O | Reference voltage ground                               |                    |  |

| REGEN      | F10    | VBAT/GNDD     | 0   | External regulator enable                              | Pulldown           |  |

| RESPWONz   | J2     | VRRTC/GNDD    | 0   | Digital baseband power-on reset (first battery plug)   |                    |  |

| RPWON      | E10    | VBAT/GNDD     | I   | Remote power-on (other than button)                    | Pullup             |  |

| RPWON2     | E12    | VBAT/GNDD     | I   | Remote power-on 2 (other than button)                  | Pullup             |  |

| SIMCK      | M4     | VRSIM/GNDD    | 0   | SIM card shifters clock output (1.8 V/3 V)             |                    |  |

| SIMIO      | K4     | VRSIM/GNDD    | I/O | SIM card shifters data (1.8 V/3 V)                     | External pullup    |  |

| SIMRST     | L4     | VRSIM/GNDD    | 0   | SIM card shifters reset output (1.8 V/3 V)             |                    |  |

| SPKN       | A7     | VCCSPK/GNDSPK | 0   | 8-Ω speaker amplifier output (–)                       |                    |  |

| SPKN       | В7     | VCCSPK/GNDSPK | 0   | 8-Ω speaker amplifier output (–)                       |                    |  |

| SPKP       | A6     | VCCSPK/GNDSPK | 0   | 8-Ω speaker amplifier output (+)                       |                    |  |

| SPKP       | В6     | VCCSPK/GNDSPK | 0   | 8-Ω speaker amplifier output (+)                       |                    |  |

| TCK        | M6     | VRIO/GNDD     | I   | Scan test clock                                        | Pulldown           |  |

| TDI        | K6     | VRIO/GNDD     | I   | Scan path input                                        | Pullup             |  |

| TDO        | H2     | VRIO/GNDD     | 0   | Scan path output                                       | 3-state            |  |

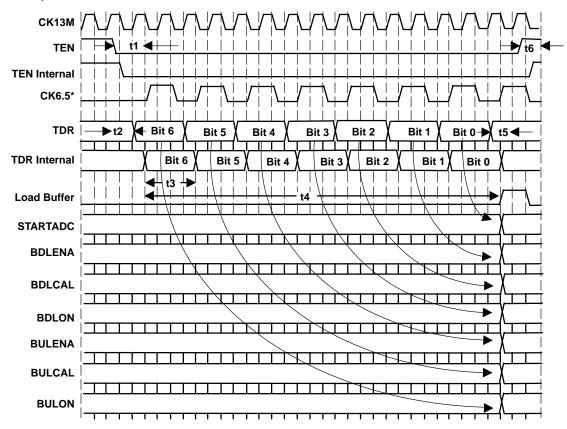

| TDR        | K2     | VRIO/GNDD     | I   | Time serial port input                                 |                    |  |

| TEN        | J4     | VRIO/GNDD     | I   | Time serial port enable                                |                    |  |

| TESTRESET  | G2     | UPR/GNDD      | I   | Reset input for test mode only                         | Pulldown           |  |

| TESTV      | C10    | VBAT/GNDA2    | 0   | Regulator output sense (reserved for test purpose)     |                    |  |

| TEST3      | L10    | VRIO/GNDD     | I/O | Special test I/O terminals                             | Pullup             |  |

| TEST4      | J9     | VRIO/GNDD     | I/O | Special test I/O terminals                             | Pullup             |  |

| TMS        | L6     | VRIO/GNDD     | I   | JTAG test mode select                                  | Pullup             |  |

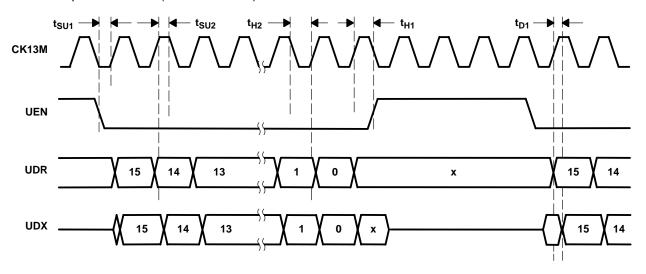

| UDR        | L3     | VRIO/GNDD     | I   | Microcontroller serial port receive data               |                    |  |

| UDX        | K3     | VRIO/GNDD     | 0   | Microcontroller serial port transmit data              | 3-state            |  |

| UEN        | M2     | VRIO/GNDD     | I   | Microcontroller serial port enable                     |                    |  |

| UPR        | G1     | UPR/GNDD      | 0   | Uninterrupted power rail output                        | External capacitor |  |

Table 2–3. Terminal Functions (Continued)

| TERM    | INAL   | QUIDE: :=c    |     |                                             |                    |

|---------|--------|---------------|-----|---------------------------------------------|--------------------|

| NAME    | NUMBER | SUPPLIES      | I/O | DESCRIPTION                                 | COMMENTS           |

| VBACKUP | F3     | VBACKUP/GNDD  | I/O | Backup battery input                        | External capacitor |

| VBAT    | M7     | VBAT/GNDA2    | I/O | Battery voltage sense input                 | External capacitor |

| VBATS   | K8     | VCCS/GNDA2    | I   | Battery voltage sense                       |                    |

| VCABB   | D11    | VCABB/GNDA2   | I/O | Input of regulator VRABB                    |                    |

| vccs    | K9     | VCCS/GNDA2    | I   | Charging current sense                      |                    |

| VCCSPK  | C6     | VCCSPK/GNDSPK | I/O | 8- $\Omega$ speaker amplifier supply        |                    |

| VCCSPK  | C7     | VCCSPK/GNDSPK | I/O | 8- $\Omega$ speaker amplifier supply        |                    |

| VCDBB   | A2     | VCDBB/GNDD    | I/O | Input of regulator VRDBB                    |                    |

| VCHG    | M8     | VCHG/GNDA2    | I/O | Charger voltage input                       | External capacitor |

| VCIO1   | L1     | VCIO/GNDD     | 1/0 | Input 1 of regulator VRIO and VRSIM         |                    |

| VCIO2   | K1     | VCIO/GNDD     | 1/0 | Input 2 of regulator VRIO and VRSIM         |                    |

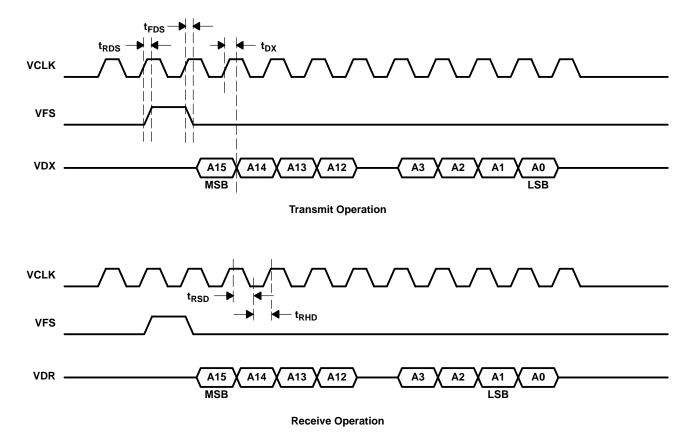

| VCK     | B4     | VRIO/GNDD     | 0   | Voiceband serial port clock                 |                    |

| VCMEM   | D2     | VCMEM/GNDD    | I/O | Input of regulator VRMEM                    |                    |

| VCRAM   | E2     | VCRAM/GNDD    | 1/0 | Input of regulator VRRAM                    |                    |

| VCUSB   | M11    | VCUSB/GNDD    | 1/0 | Input of regulator VRUSB                    |                    |

| VDR     | B2     | VRIO/GNDD     | -   | Voiceband serial port receive data          |                    |

| VDX     | D4     | VRIO/GNDD     | 0   | Voiceband serial port transmit data         |                    |

| VFS     | B3     | VRIO/GNDD     | 0   | Voiceband serial port frame synchronization |                    |

| VLMEM   | G3     | UPR/GNDD      | _   | Select output voltage of VRMEM              |                    |

| VLRTC   | B5     | UPR/GNDD      | _   | Select output voltage of VRRTC and VRDBB    |                    |

| VLRTC0  | C5     | UPR/GNDD      | -   | Select output voltage of VRRTC and VRDBB    |                    |

| VRABB   | D12    | VRABB/GNDA    | 0   | Regulator VRABB output                      | External capacitor |

| VRDBB   | А3     | VRDBB/GNDD    | 0   | Regulator VRDBB output                      | External capacitor |

| VREF    | L11    | VRABB/REFGND  | I/O | Reference voltage (1.18 V)                  | External capacitor |

| VRIO1   | M1     | VRIO/GNDD     | 0   | Regulator VRIO output 1                     | External capacitor |

| VRIO2   | L2     | VRIO/GNDD     | 0   | Regulator VRIO output 2                     | External capacitor |

| VRMEM   | D1     | VRMEM/GNDD    | 0   | Regulator VRMEM output                      | External capacitor |

| VRRAM   | F1     | VRRAM/GNDD    | 0   | Regulator VRRAMoutput                       | External capacitor |

| VRRTC   | H1     | VRRTC/GNDD    | 0   | Regulator VRRTC output                      | External capacitor |

| VRSIM   | M3     | VRSIM/GNDD    | 0   | Regulator VRSIM output                      | External capacitor |

| VRUSB   | M12    | VRUSB/GNDD    | 0   | Regulator VRUSB output                      | External capacitor |

| VSDBB   | A1     | VRDBB/GNDD    | - 1 | Regulator VRDBB input feedback              |                    |

# 3 Functional Description

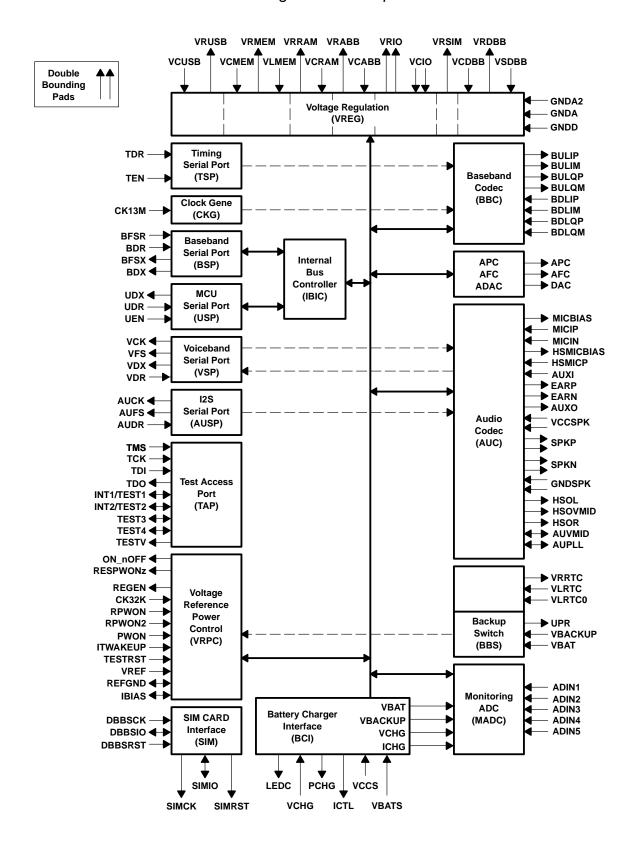

This section describes the functional blocks that comprise the TWL3016 device. Figure 3–1 is a block diagram of the device.

Figure 3-1. TWL3016 Functional Block Diagram

#### 3.1 Audio Codec

The audio codec (AUC) consists of a voice coder-decoder (codec) dedicated to GSM applications and an audio stereo line. The voice codec circuit processes analog audio components in the uplink path and transmits this signal to the DSP speech coder through the voice serial port (VSP). In the downlink path, the codec converts the digital samples of speech data received from the DSP via the VSP port into analog audio signals. The voice codec supports an 8-kHz (default) or a 16-kHz sampling frequency. The stereo audio path converts audio component data received from the I2S serial interface (AUSP) into analog audio.

The AUC includes input amplifiers for microphones (headset, phone, auxiliary) and output amplifiers (stereo/mono headset, phone speaker,  $8-\Omega$  speaker, auxiliary).

The AUC also performs the programmable gain, volume control, and side-tone functions for the uplink and downlink path of the voice codec. A common programmable gain and two independent volume controls are available for the right and left channels of the stereo path.

#### 3.2 Baseband Codec

The baseband codec (BBC) is composed of a baseband uplink (BUL) path and a baseband downlink (BDL) path.

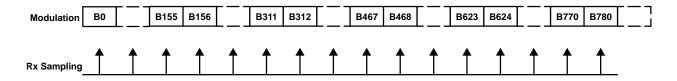

The BUL path modulates the data bursts coming from the DSP via the baseband serial port (BSP). Modulation is performed by a Gaussian minimum shift keying (GMSK) modulator, according to GSM specification 5.04. The GMSK modulator, which is implemented digitally, generates the in-phase (I) and quadrature (Q) components. These components are converted into analog baseband by two 10-bit DACs and filtered by third-order low-pass filters. The BUL path includes secondary functions such as dc offset calibration and I/Q gain unbalance.

The BDL path converts the baseband analog I and Q components from the RF receiver into digital samples. The resulting signals are filtered through a digital FIR to isolate the desired data from the adjacent channels. During reception of the burst I and Q components, the digital data are sent to the DSP via the BSP at a rate of 270.833 kHz. The BDL path includes a dc offset calibration.

Timing windows of the BUL and BDL paths are controlled through the time serial port (TSP) by the TPU of the digital baseband (DBB) device.

Implementation of the BBC allows multislot and full-duplex operation.

#### 3.3 Low-Dropout Linear Voltage Regulator

Several low-dropout (LDO) regulators perform linear voltage regulation. These regulators, connected to the main battery, supply power to:

- Internal analog blocks

- Internal digital blocks and the DBB I/Os

- The DBB core

- External memories

- SIM card and SIM card drivers

All these regulators allow a low current consumption working mode, SLEEP mode, but with a reduced current capability.

A regulator supplies USB I/Os, with an input voltage derived from an USB connector.

The last LDO (VRRTC) is a programmable regulator that generates the supply voltages for the real time clock (32 kHz) of the DBB processor and dedicated I/Os. The main or backup battery supplies VRTC, using the uninterrupted power rail (UPR). This LDO has an ultralow current consumption.

#### 3.4 Backup Battery Switch

The backup battery switch (BBS) generates at its output an uninterrupted power rail (UPR) to supply the minimum necessary circuitry of the power-control functions continuously, either from the main battery or from the backup battery. This UPR is connected to the UPR output terminal for decoupling purposes. No external load is allowed on UPR.

#### 3.5 SIM Card Shifters (SIMS)

To allow the use of both 1.8-V and 3-V SIM card types, a SIM level-shifter module in the TWL3016 device interfaces the SIM signals (DBBSRST, DBBSIO, and DBBSCK) at a constant VRIO level from the DBB device with the SIM card (SIMRST, SIMIO, and SIMCK) at a 1.8-V or 3-V level depending on SIM type.

#### 3.6 Monitoring ADC

The monitoring ADC (MADC) consists of a 10-bit analog-to-digital converter (ADC) combined with an 9-input analog multiplexer. Five of the nine inputs are available externally, and the remaining four inputs are dedicated to main battery voltage, backup battery voltage, charger voltage, and charger current monitoring. Of the five available external inputs, three are standard inputs, and the two that are associated with current sources are intended for battery temperature and battery type measurements.

Conversion requests, input/output channels, and results reading can be performed either through the BSP, through the USP, or through the TSP interface.

#### 3.7 Voltage Reference/Power-On Control

The external resistor connected between the IBIAS and REFGND terminals sets the value of the bias currents of the analog functions from the band-gap voltage.

The voltage reference/power-on control (VRPC) block controls the power on, power off, switch on, and switch off sequences.

Some block functions are performed even in the off state. These permanent functions ensure the wake-up of the device, such as, ON/OFF button detection or charger detection.

Interrupt INT2 is generated either for the following events: PWON, RPWRON, RPWON2, a charger plug/unplug is detected, or an USB plug/unplug is detected while the device is in power on. Interrupt INT1 is generated when abnormal low battery voltage condition is detected. See Section 4.6.7, *Interrupt Handling*.

#### 3.8 Baseband Serial Port

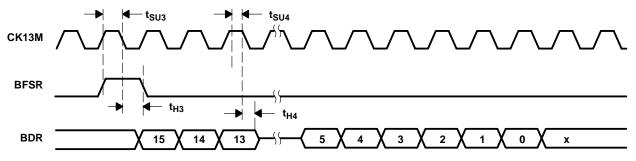

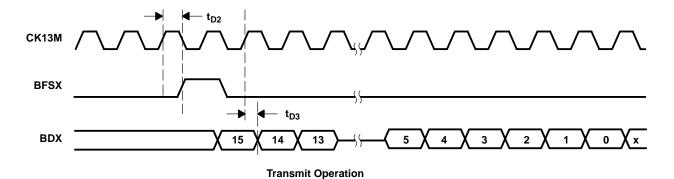

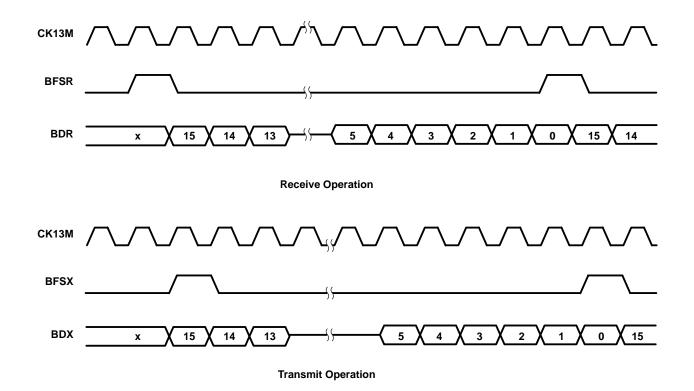

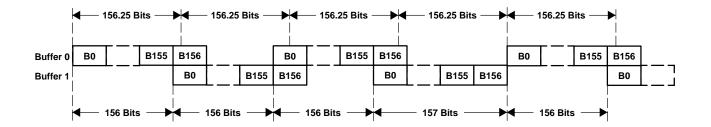

The baseband serial port (BSP) is a bidirectional (transmit/receive) serial port. Both receive and transmit operations are double-buffered and permit a continuous communication stream. Format is a 16-bit data packet with transmit and receive frame synchronization signals. In the receive mode, the data (BDR) and the frame synchronization signal (BFSR) are given by the DBB device. In the transmit mode, the data (BDX) and the frame synchronization signal (BFSX) are given by the TWL3016 device. The CK13M master clock is used as a clock for both transmit and receive modes.

The BSP allows read and write access of all internal registers under the arbitration of the internal bus controller. But its transmit path is allocated to the BDL path during burst reception for I and Q data transmissions.

#### 3.9 Time Serial Port

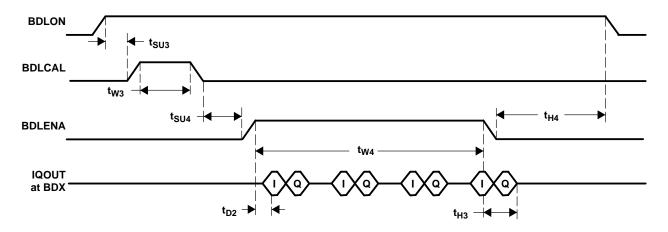

The time serial port (TSP) controls in real time the radio activation windows of the TWL3016 device: BUL power-on, BUL calibration, BUL transmit, BDL power-on, BDL calibration, BDL receive, and the ADC conversion start.

These real-time control signals are processed by the TPU of the DBB device and transmitted serially to the TWL3016 device via the TSP, which consists of a very simple two-terminal serial port. The TEN terminal is an enable, the TDR terminal is the data receive. The CK13M master clock divided by two is used internally as the clock for this serial port.

#### 3.10 Microcontroller Serial Port

The microcontroller serial port (USP) is a bidirectional (transmit/receive) synchronous serial port. It consists of three terminals: data transmit (UDX), data receive (UDR), and port enable (UEN). The clock signal is the CK13M master clock. Transfers are initiated by the external microcontroller, which pushes data into the USP via the UDR, while synchronous data contained in the transmit buffer of the USP is pushed out via the UDX. A minimum of eight rising edges of the CK13M or CK32K clocks (depending on the status of bit 6 (ACTIVMCLK) in the power down register) separate two consecutive USP accesses.

The USP allows read and write access of all internal registers under the arbitration of the internal bus controller.

#### 3.11 Voiceband Serial Port

The voice serial port (VSP) is a bidirectional (transmit/receive) configurable serial port. It consists of four terminals: data transmit (VDX), data receive (VDR), the frame synchronization signal (VFS), and the clock signal (VCK). Both receive and transmit operations are double-buffered and permit a continuous communication stream. Format is a 16-bit data packet with frame synchronization. The serial interface may be configured for the following two operating modes:

- 8-kHz frame synchronization signal (default mode) and 500-kHz (default)/1-MHz programmable master clock signal

- 16-kHz frame synchronization signal and 500-kHz (default)/2-MHz programmable master clock signal

#### 3.12 Stereo Audio (I2S) Serial Port

The audio serial port (AUSP) is a synchronous serial port. It consists of three terminals: data receive (AUDR), the left/right frame synchronization signal (AUFS), and the clock signal (AUCK). Format is a 2\*20-bit data packet with a programmable sampling frequency ( $F_S = [8-48k] \, Hz$ ). The TWL3016 device delivers a  $40*F_S$  master data clock. The stereo audio interface allows the I2S reception mode.

#### 3.13 Automatic Frequency Control

The automatic frequency control (AFC) function consists of a digital-to-analog converter (DAC) optimized for high-resolution dc conversion. The AFC controls the frequency of the GSM 13-MHz oscillator to maintain mobile synchronization on the base station and to allow proper transmission and demodulation.

#### 3.14 Automatic Power Control

The automatic power control (APC) generates an envelope signal to control the power ramp up, power ramp down, and power level of the radio burst. The APC structure is intended to support single-slot and multislot transmissions with smooth power transitions when consecutive bursts are transmitted at different power levels.

The APC includes a DAC and a RAM, in which the shape of the edges (ramp up and ramp down) of the envelope signals are stored digitally. This envelope signal is converted to an analog signal by a 10-bit DAC.

Timing of the APC is generated internally and depends on the real-time signals coming from the TSP and the contents of two registers that control the relative position of the envelope signal versus the modulated I and Q components.

#### 3.15 Auxiliary DAC

The auxiliary DAC (ADAC) is a general-purpose 10-bit DAC.

#### 3.16 High Voltage (20 V) Battery Charger Interface

The TWL3016 battery charger interface (BCI) controls the charging of either a 1-cell Li-lon battery or a 3-series Ni-MH/Ni-Cd cell battery with the support of the microcontroller (the DBB device).

The battery is monitored using the 10-bit ADC converter from the MADC to measure the battery voltage, battery temperature, battery type, battery charge current, and battery charger input voltage.

The magnitude of the charging current is set by 8 bits of a programming register converted by the 8-bit DAC, whose output sets the reference input of the charging current control loop. The magnitude of the charging voltage is set by 10 bits of a programming register converted by a 10-bit DAC, whose output sets the reference input of the charging voltage control loop.

The BCI also performs some auxiliary functions. These functions are battery precharge, battery over-temperature detection, battery over-voltage detection, battery end-of-charge current detection, and back-up.

An external LED may be driven depending of the charger status. When the TWL3016 device is in off or sleep mode, the LED control follows the precharge state. When the TWL3016 device is in active mode, the LED is controlled through bit 5 (LEDC) in the battery control 2 register (see Section 5.3.7.4).

The BCI is under register control. These registers can be programmed either through the BSP or through the USP.

## **4 Detailed Description**

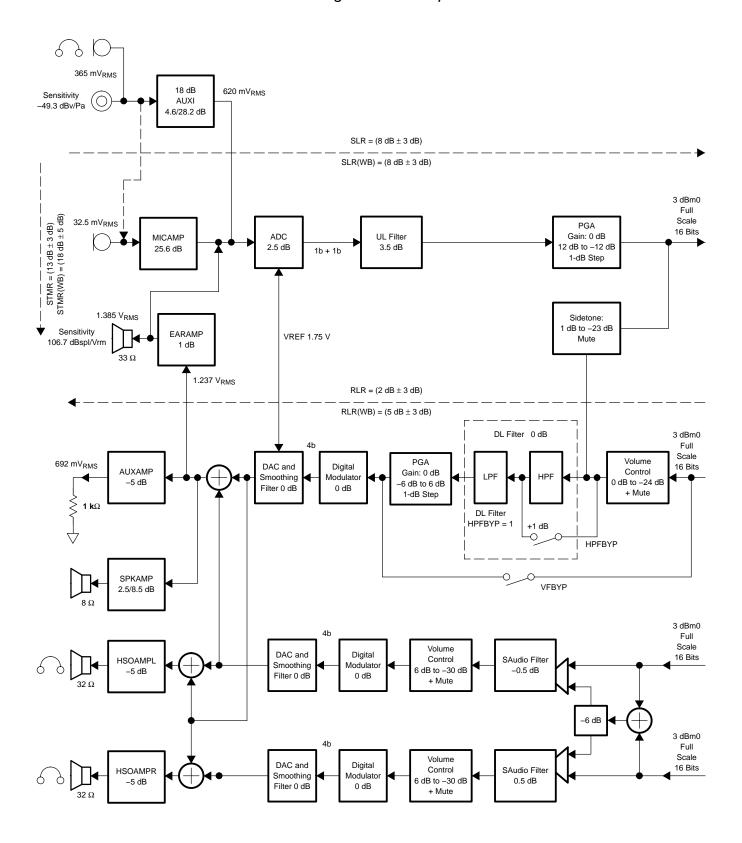

#### 4.1 Audio Codec

The audio codec consists of a voice codec dedicated to the GSM application and an audio stereo line. The voice codec circuitry processes analog audio components in the voice uplink (VUL) path and applies this signal to the voice signal interface for eventual baseband modulation. In the voice downlink (VDL) path, the codec circuitry changes voice component data received from the voice serial interface (VSP) into analog audio. The voice codec supports an 8-/16-kHz sampling frequency. The stereo audio path converts audio component data received from the I2S serial interface into analog audio. The following paragraphs describe these uplink/downlink and audio stereo functions in more detail.

Figure 4-1. Audio Codec Block Diagram

Table 4–1 shows the available signals on the audio codec outputs, depending on the programmed configuration.

Table 4-1. Audio Codec Output Signals

| SERIAL<br>INTERFACE | EARAMP       | AUXAMP       | SPKAMP       | HSOAMPL                        | HSOAMPR                         |

|---------------------|--------------|--------------|--------------|--------------------------------|---------------------------------|

| VSP                 | Voice speech | Voice speech | Voice speech | Voice speech                   | Voice speech                    |

| I2S                 | Audio mono   | Audio mono   | Audio mono   | Audio mono                     | Audio mono                      |

| VSP                 | Voice speech | Voice speech | Voice speech | Voice speech                   | Voice speech                    |

| +                   | +            | +            | +            | +                              | +                               |

| I2S                 | Audio mono   | Audio mono   | Audio mono   | Audio stereo left / Audio mono | Audio stereo right / Audio mono |

#### 4.1.1 Voice Uplink Path

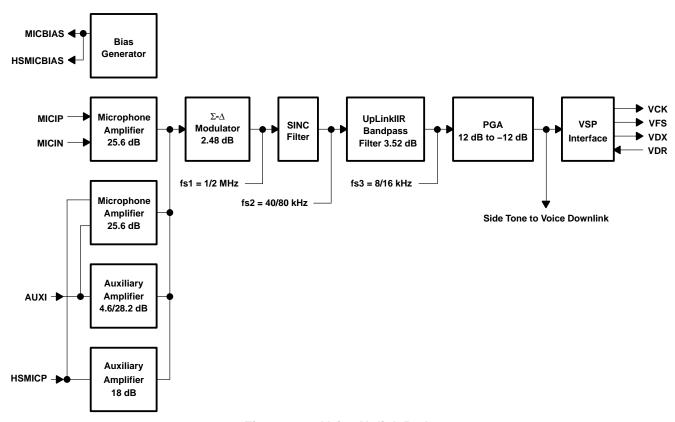

The VUL path includes two input stages. The first stage is a microphone amplifier, compatible with electret microphones containing an FET buffer with open drain output. The microphone amplifier has a gain of typically 25.6 dB and a bias generator provides an external voltage of 2.0 V to 2.5 V to bias the microphone (MICBIAS terminal). The auxiliary audio input can be used as an alternative source for higher level of speech signals. This stage performs single-ended-to-differential conversion and provides a programmable gain of 4.6 dB or 28.2 dB. The input of the auxiliary audio stage and the microphone biasing voltage can also be available on the headset microphone terminals (HSMIC and HSMICBIAS). When the auxiliary audio input is used, the microphone input is disabled and powered down. The auxiliary audio input and the headset microphone gain stage can't be active at the same time. The auxiliary audio input and the headset microphone input can be used as differential inputs of the microphone amplifier, the microphone input terminals are then set to a high impedance state and a biasing voltage can be available on the HSMICBIAS or MICBIAS terminal.

The resulting fully differential signal is fed to the analog-to-digital converter (ADC) which is determined by the value of the internal voltage reference.

The analog-to-digital conversion is performed by a third-order  $\Sigma$ - $\Delta$  modulator with a sampling rate of 1 MHz/2 MHz. Output of the ADC is fed to a speech digital filter, which performs the decimation down to 8 kHz/16 kHz and band-limits the signal with both low-pass and high-pass transfer functions. Programmable gain can be set digitally from –12 dB to +12 dB in 1-dB steps and is programmed with bits 4–0 (VULPG(4:0)) of the voiceband uplink register (see Section 5.3.10.4). The speech samples are then transmitted to the DSP via the VSP at a rate of 8 kHz/16 kHz. Programmable functions of the VUL path, power-up, input selection, and gain are controlled using the BSP or the USP serial interfaces. The VUL path can be powered down using bit 0 (VULON) of the power down register (see Section 5.3.3.3).

Figure 4-2. Voice Uplink Path

#### 4.1.2 Voice Downlink Path

The VDL path receives speech samples at the rate of 8 kHz/16 kHz from the DSP via the VSP and converts them to analog signals to drive the external speech transducer.

The digital speech coming from the DSP is first fed to a speech digital filter that has two functions. The first function interpolates the input signal and increases the sampling rate from 8 kHz/16 kHz up to 40 kHz/80 kHz to allow the digital-to-analog conversion to be performed by an over-sampling digital modulator. The second function band-limits the speech signal with both low-pass and high-pass transfer functions. The filter and PGA gain can be bypassed by programming bit 9 (VFBYP) in the voiceband control register 1 (see Section 5.3.10.1). The highpass of the speech downlink filter can be bypassed using bit 3 (HPFBYP) of the audio control register (see Section 5.3.10.6).

The interpolated and band-limited signal is fed into a second order  $\Sigma$ - $\Delta$  digital modulator sampled at 1 MHz or 2 MHz to generate a 4-bit (9-level) over-sampled signal. This signal is then passed through a dynamic element matching block and then to a 4-bit digital-to-analog converter (DAC).

Due to the over-sampling conversion, the analog signal obtained at the output of the 4-bit DAC is mixed with a high frequency noise. Because a 4-bit digital output is used, a first-order RC filter (included in the output stage) is enough to filter this noise.

The volume control and the programmable gain are performed in the TX digital filter. Volume control is performed in steps of 6 dB from 0 dB to -24 dB. In the mute state, attenuation is higher than 40 dB. A fine adjustment of gain is possible from -6 dB to +6 dB in 1-dB steps to calibrate the system depending on the earphone characteristics. This configuration is programmed with the voiceband control register.